# 600 Series 6U CPCI Redundant Backplane/Midplane & Chassis

User Manual

Sales Office: +1 (301) 975-1000 Technical Support: +1 (301) 975-1007 E-mail: support@patton.com WWW: www.patton.com

> Document Number: 600001U Rev. A Part Number: 07M600001-A Revised:November 13, 2001

Patton Electronics Company, Inc. 7622 Rickenbacker Drive Gaithersburg, MD 20879 USA tel: +1 (301) 975-1000 fax: +1 (301) 869-9293 support: +1 (301) 975-1007 web: www.patton.com e-mail: support@patton.com

Copyright © 2000, 2001, Patton Electronics Company. All rights reserved.

The information in this document is subject to change without notice. Patton Electronics assumes no liability for errors that may appear in this document.

Any software described in this document is furnished under license and may be used or copied only in accordance with the terms of such license.

# **Contents**

|   | Contents                                            | 3    |

|---|-----------------------------------------------------|------|

|   | About this guide                                    | 7    |

|   | Audience                                            | 7    |

|   | Structure                                           | 7    |

|   | Precautions                                         | 8    |

|   | Style conventions used in this document             | 8    |

|   | Typographical conventions used in this document     | 9    |

|   | General conventions                                 | 9    |

|   | Mouse conventions                                   | 9    |

|   | Bibliography                                        | 10   |

| 1 | Introduction                                        | . 11 |

|   | Product features and benefits                       |      |

|   | What is CompactPCI?                                 |      |

|   | About Patton Electronics Company                    |      |

| 2 | Chassis specifications                              |      |

| 2 | 6U CPCI subrack                                     |      |

|   | Chassis description, front side                     |      |

|   | Chassis description, rear side                      |      |

|   | Electromagnetic compatibility (EMC)                 |      |

|   | Electrostatic discharge (ESD) protection            |      |

|   | Materials specifications—Models 601 and 602 chassis |      |

|   | Patton Electronics' product interfaces              |      |

|   | Model 5406 6U Redundant Backplane/Midplane          |      |

|   | Model 5250 Series Power Supply Module               |      |

|   | Model 5502 6U Alarm Interface Module                |      |

| 3 | Installation checklist                              | 23   |

| 5 | 6U quick set-up checklist                           |      |

| 4 | System Architecture                                 |      |

| 4 | CompactPCI form factor                              |      |

|   | Board front panels                                  |      |

|   | Transition Boards                                   |      |

|   | Pin and socket connectors                           |      |

|   | J1/P1 & J2/P2 connectors                            |      |

|   | J3/P3 through J5/P5 connector                       |      |

|   | Reserved Pins                                       |      |

|   | Power Pins                                          |      |

|   | Backplane Architecture                              |      |

|   | Signaling Environment                               |      |

|   | Changing the signaling environment voltage          |      |

|   | Sharpene are admining entriconnent fortuge          |      |

|   | Slot Designation                          |    |

|---|-------------------------------------------|----|

|   | Bus segments                              |    |

|   | Backplane signals                         |    |

|   | Alarms                                    |    |

|   | Backplane power distribution              | 41 |

|   | External power connections                |    |

|   | Backplane power bugs and connectors       |    |

|   | In-rack power connections                 |    |

|   | Front panel keying for power supplies     |    |

|   | Power decoupling                          |    |

|   | Hot-Swap Capability                       |    |

|   | Hot-Swap Insertion Sequence               |    |

|   | Hot-swap removal sequence                 | 47 |

|   | Keying of CPCI backplanes and boards      |    |

|   | Backplane connector keys                  |    |

|   | Front panel and cardguide keys            |    |

| 5 | CT H.110 Bus Architecture                 | 51 |

| 1 | CT H.110 Bus                              |    |

|   | H.110 TDM bus P4 pins                     |    |

|   | Telecom power bus P4 pins                 |    |

|   | Telecom ringing bus P4 pins               |    |

|   | Platform power bus P4 pins                |    |

|   | Shelf enumeration bus P4 pins             |    |

|   | Geographic address P4 pins                |    |

|   | Reserved pins on P4                       |    |

|   | Frame ground bus P4 pins                  |    |

|   | Not populated pins and pads on P4         |    |

|   | Power fail sense bus pins on P4           |    |

|   | Key electrical considerations             |    |

|   | User-defined CT I/O on P5                 |    |

| 6 | Maintenance                               | 61 |

| U | Troubleshooting                           |    |

|   | System won't power up                     |    |

|   | Hot-swap of power supply fails            |    |

|   | No-load condition generates a false alarm |    |

|   | Warranty Information                      |    |

|   | Service                                   |    |

|   |                                           |    |

| A | Glossary of Terms                         |    |

|   | С                                         |    |

|   | CFM                                       |    |

|   | CSA                                       |    |

|   | CT                                        |    |

|   | D                                         | 66 |

| Dual Redundant |    |

|----------------|----|

| Е              | 66 |

| ECTF           |    |

| EIA            |    |

| EMC            |    |

| EMI            |    |

| EN             |    |

| Enumeration    |    |

| ESD            |    |

| Eurocard       |    |

| Н              |    |

| Hot-Swap       |    |

| НР             |    |

| I              |    |

| IDE            |    |

| IEC            |    |

| IEEE           |    |

| IN/C           |    |

| ISA            |    |

| К              |    |

| Keying         |    |

| N              |    |

| N+1 Redundant  |    |

| NEBS           |    |

| NP             |    |

| Р              |    |

| PCI            |    |

| PCI SIG        |    |

| PICMG          |    |

| Platform       |    |

| S              |    |

| SELV           |    |

| S-HAZ          |    |

| Shroud         |    |

| Τ              |    |

| TDM            |    |

| TNV            |    |

| U              |    |

| U              |    |

| W              |    |

| Warm-Swap      | 68 |

# About this guide

This manual is a comprehensive hardware reference tool for the Patton Electronics 6U CPCI Redundant Backplane/Midplane and Chassis line of products.

## **Audience**

This guide is intended for the following users:

- System developers installing and integrating the products into their systems

- Operators

- Installers

- Maintenance technicians

## Structure

This guide contains the following chapters and appendices:

- Chapter 1, "Introduction"—provides an overview of the product, about Patton Electronics, warranty, and service information.

- Chapter 2, "Chassis specifications"-provides an overview of the chassis features.

- Chapter 3, "Installation checklist"—provides a quick set-up checklist for installing the Model 600.

- Chapter 4, "System Architecture"—provides an overview of CompactPCI specifications, as well as a more in-depth description of the product's features.

- Chapter 5, "CT H.110 Bus Architecture"—defines the CT Bus configured on the J4/P4 connector, when applicable.

- Chapter 6, "Maintenance"—provides a quick set-up checklist, tips for troubleshooting, warranty information, and where to get help.

- Appendix A, "Glossary of Terms"—defines terms and acronyms used in this document.

For best results, read the contents of this guide before you install the enclosure.

### About this guide

## Precautions

Notes and cautions, which have the following meanings, are used throughout this guide to help you become aware of potential problems. *Warnings* relate to personal injury issues, and *Cautions* refer to potential property damage.

**Note** Calls attention to additional or noteworthy information or tips.

The shock hazard symbol and WARNING heading indicate a potential electric shock hazard. Strictly follow the warning instructions to avoid injury caused by electric shock.

The alert symbol and WARNING heading indicate a potential safety hazard. Strictly follow the warning instructions to avoid personal injury.

The shock hazard symbol and CAUTION heading indicate a potential electric shock hazard. Strictly follow the instructions to avoid property damage caused by electric shock.

The alert symbol and CAUTION heading indicate a potential hazard. Strictly follow the instructions to avoid property damage.

This symbol and the CAUTION heading indicates a situation where damage to equipment can be caused by electrostatic discharge.

This symbol and the IMPORTANT heading provides information which should be followed for best results when installing, configuring, or operating the Patton product.

# Style conventions used in this document

Tables contain information of a descriptive nature. For example, pin assignments or signal description.

Cross-references, figure titles, and table titles are in italicized and hyperlinked. This means that if you have the on-line version of this document, you can click on the cross-reference and it will "jump" you to that reference within the document. This feature only works with references to sections/tables/figures within this document. References to other documents (for example, *PICMG 2.5 R1.0 CompactPCI Computer Telephony Specification*) are not hyperlinked.

The symbols "/" and "#" indicate signals that are active low.

Specific safety-related terms, traceable to certain safety regulatory agency requirements (i.e., IEC950 and harmonized derivative specifications) are used within this manual. Refer to the referenced document for a definition of these terms.

# Typographical conventions used in this document

This section describes the typographical conventions and terms used in this guide.

### **General conventions**

The procedures described in this manual use the following text conventions:

| Convention             | Meaning                                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------|

| Futura bold type       | Indicates the names of menu bar options.                                                                        |

| Italicized Futura type | Indicates the names of options on pull-down menus.                                                              |

| Futura type            | Indicates the names of fields or windows.                                                                       |

| Garamond bold type     | Indicates the names of command buttons that execute an action.                                                  |

| < >                    | Angle brackets indicate function and keyboard keys, such as <shift>, <ctrl>, <c>, and so on.</c></ctrl></shift> |

| Are you ready?         | All system messages and prompts appear in the Courier font as the system would display them.                    |

| % dir *.*              | Bold Courier font indicates where the operator must type a response or command                                  |

### Mouse conventions

The following conventions are used when describing mouse actions:

| Convention         | Meaning                                                                                                                                                                                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Left mouse button  | This button refers to the primary or leftmost mouse button (unless you have changed the default configuration).                                                                                                                                                            |

| Right mouse button | This button refers the secondary or rightmost mouse button (unless you have changed the default configuration).                                                                                                                                                            |

| Point              | This word means to move the mouse in such a way that the tip of the pointing arrow on the screen ends up resting at the desired location.                                                                                                                                  |

| Click              | Means to quickly press and release the left or right mouse button (as instructed in the procedure). Make sure you do not move the mouse pointer while clicking a mouse button.                                                                                             |

| Double-click       | Means to press and release the same mouse button two times quickly                                                                                                                                                                                                         |

| Drag               | This word means to point the arrow and then hold down the left or right mouse but-<br>ton (as instructed in the procedure) as you move the mouse to a new location.<br>When you have moved the mouse pointer to the desired location, you can release<br>the mouse button. |

### Table 2. Mouse conventions

# **Bibliography**

The following publications are used in conjunction with this manual.

- ECTF H.110 (CT Bus) Specification (Revision 1.0)

- CompactPCI Hot Swap Specification—PICMG 2.12 (Revision 1.0)

- CompactPCI Specification—PICMG 2.0 (Revision 2.1)

- Keying of CompactPCI Boards and Backplanes Specification—PICMG 2.10 (Revision 1.0)

- IEC950, Safety of Information Technology Equipment, including Electrical Business Equipment

- IEC 61076-4-101 (1995-05), Specification for 2mm Connector System

- IEEE 1101.10, IEEE Standard for Additional Mechanical Specifications for Microcomputers using IEEE 1101.1 Equipment Practice

# Chapter 1 Introduction

# Chapter contents

| Product features and benefits    | 12 |

|----------------------------------|----|

| What is CompactPCI?              | 12 |

| About Patton Electronics Company |    |

| noout Futton Electronico Company |    |

### 1 • Introduction

## **Product features and benefits**

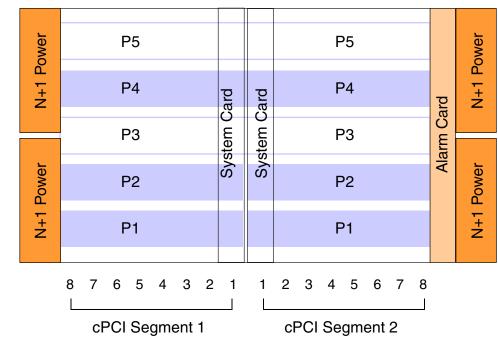

Thank you for purchasing the Patton Electronics 600 Series 6U CPCI Redundant Backplane/Midplane and Chassis. The 600 Series chassis is a 21-slot redundant system. The backplane/midplane provides two, electrically separate, 8-slot CPCI bus segments on P1/P2. It also provides a 17-slot common H.110 bus on P4.

The backplane/midplane is configured to accept four Patton Electronics 3U plug-in supplies for N+1 power redundancy. The system can provide 600 W of online power, with one 200 W hot standby unit for fault tolerant operation. The backplane/midplane supports all feed-through with rear A/B shrouds on RP3, RP4, and RP5, and the 14 layer design provides excellent power distribution and signal integrity.

The 600 Series chassis complies with the *PICMG 2.0 R3.0 CompactPCI Specification*, and *PICMG 2.5, ECTF H.110 (CT Bus) Specification* (Rev. 1.0), making it an excellent choice for redundant, fault tolerant applications

# What is CompactPCI?

CompactPCI (Peripheral Component Interconnect) is a high-performance industrial computer platform based on the standard PCI electrical specification in rugged 3U or 6U Eurocard-style packaging, with a high-quality 2mm metric pin and socket connector.

CompactPCI is an open specification supported by the PICMG (PCI Industrial Computer Manufacturers Group), which is a consortium of companies involved in utilizing PCI for embedded applications.

Distinct advantages of CompactPCI ("CPCI") include:

- Cost/time savings—Because it is electrically compatible with PCI, CPCI allows designers to tap into the wealth of available hardware and software. CPCI provides a substantial reduction in engineering and manufacturing costs because off-the-shelf items can be shipped to meet your configuration needs and delivery schedules.

- Rugged and reliable—The Eurocard-style packaging—which includes two-piece shielded connectors for better reliability and vertical card orientation for better cooling—provides a robust system based on a sub-rack backplane architecture.

- Flexibility—CPCI allows either 32- or 64-bit PCI, plus offers an open architecture. Additional connectors are defined for adding standard or proprietary buses or other needs. Hybrid CPCI systems allow bridging to other buses or custom applications.

- Hot-swap capability—Boards can be hot-swapped without disrupting operation, a critical feature in realtime and high-availability applications.

CompactPCI is rapidly becoming the backbone of today's high-performance, embedded systems. It is ideally suited for telecommunications, computer telephony, real-time machine control, industrial automation, real-time data acquisition, instrumentation, military systems and other applications requiring high speed computing and modular, robust packaging design.

# **About Patton Electronics Company**

Patton Electronics excels in the design, development and production of Embedded Data Communications and Telecommunications Platforms based on open system bus architecture standards (for example, CPCI and VME). These platforms form a significant part of the infrastructure for today's information technology revolution—including the emergence of new packet-based (IP) global communication networks.

Datacom/Telecom platforms require robust and reliable packaging solutions that address key technology issues, such as line density, thermal management, power distribution, scalability, and regulatory compliance. With an increasing number of applications demanding downtime measured in minutes rather than hours, special consideration has to be given to enclosure system functionality. Patton Electronics' full line of enclosure solutions are designed specifically to meet industry's stringent high availability requirements where redundant operation, quick accessibility and high reliability are essential. Patton has a broad engineering background in the development of these technologies for advanced circuit and packet-switched telecommunications systems running voice, data and video applications for commercial and government customers.

Patton offers a wide range of platforms consisting of standard rack/chassis, high speed backplane, power, thermal management, single board computer (SBC) and alarm/network interface products for commercial, voice/data communications, and government/military system applications. Patton Electronics is ISO-9001 Certified. 1 • Introduction

600 Series 6U CPCI Chassis User Manual

# Chapter 2 Chassis specifications

# Chapter contents

| 16 |

|----|

| 17 |

| 18 |

| 19 |

| 20 |

| 21 |

| 22 |

| 22 |

| 22 |

| 22 |

|    |

### 2 • Chassis specifications

# **6U CPCI subrack**

The 600 Series chassis are modular 6U x 19 inch rackmount subrack-type packaging systems suitable for open bus architectures such as CPCI, or custom bus applications. The rugged, rack-mounted 6U CPCI chassis is ideal for telecom, defense, industrial, and commercial environments, and excels in its ease of access, superior cooling, and power distribution. The base unit is adaptable to a wide array of product configurations.

This chapter details the Model 601 6U chassis with 80mm transition module section. The Model 602 does not have the transition module section, making it only 7.25 inches in maximum depth. A listing of the differences between Models 601 and 602 is provided in section "Materials specifications—Models 601 and 602 chassis" on page 21.

Product features include:

- ✓ Full dimensional compatibility with CompactPCI (PICMG 2.0 R3.0) and IEEE-1101.10.

- ✓ EMI shielding on entire assembly, with continuous chassis ground.

- ✓ Lightweight and durable aluminum construction, suitable for rugged environments.

- ✓ Five standard colors (additional colors are also available). Standard powder coating finish.

- ✓ Front mounting flanges for 19 in. rack mount environments.

# Chassis description, front side

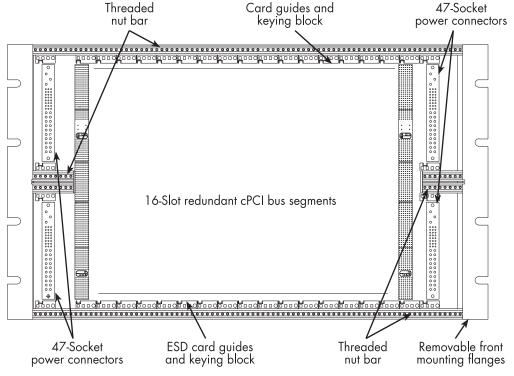

The Model 601, CPCI 6U chassis is 10.50 inches high, by 19 inches wide (standard EIA rack mount, with removable rack mount flanges), by 12 inches deep (maximum). There are sixteen 6U x 160mm slots, (see

figure 1) providing two, electrically separate, CPCI bus segments, at the front of the chassis. Front-entry boards, in accordance with PICMG 2.0 R3.0 CompactPCI specifications, are plugged-in at these slots.

Figure 1. Front view of the Model 601 6U CPCI chassis

The front of the chassis also provides four 3U x 160mm slots to mount up to four Patton power supply modules configured for external DC input, or other CPCI compatible power modules for N+1 power redundancy. The system can provide 600 W of online power, with one 200 W hot standby unit for fault tolerant operation.

**Note** The chassis guide rails are 1/2HP offset for plug-able power supplies to meet the standards of *PICMG 2.11, R1.0 CompactPCI Power Inter-face "Draft" Specification.* That is to say, the card guide's slot and injector/ejector PCB mounting surface are shifted 0.1 inch to the right of the card. Card guides are green in color.

All slots provide 4HP module spacing and are on 0.80 in. centers (except for the power connector slots noted above). Card guides are molded plastic with metallic ESD contacts at the bottom of the chassis (see section "Electrostatic discharge (ESD) protection" on page 19) per CompactPCI PICMG 2.0 R3.0 & IEEE 1101.10. Cardguides provide keying and alignment in accordance with IEEE 1101.10, section 8. See "Keying of CPCI backplanes and boards" on page 48 for more information on keying.

### 2 • Chassis specifications

# Chassis description, rear side

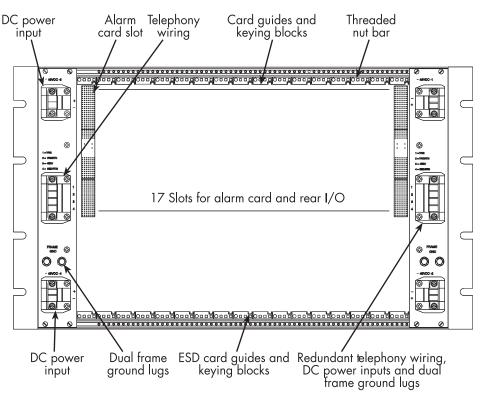

The rear of the Model 601 chassis provides seventeen 6U x 80mm slots for an Alarm card and/or other CPCI transition modules for rear-panel I/O (see figure 2). See "Transition Boards" on page 27 for more information.

Figure 2. Rear view of the Model 601 6U CPCI chassis

All slots provide 4HP module spacing and are on 0.80 in. centers. Card guides are molded plastic with metallic ESD contacts at the bottom of the chassis (See "Electrostatic discharge (ESD) protection" on page 19) per *CompactPCI PICMG 2.0 R3.0 & IEEE 1101.10*. Cardguides provide keying and alignment in accordance with IEEE 1101.10, section 8. See "Keying of CPCI backplanes and boards" on page 48 for more information on keying.

**Note** See Table 8 on page 42 for more information on the connectors

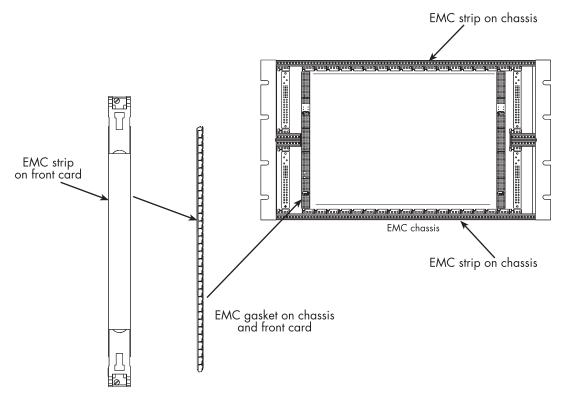

## Electromagnetic compatibility (EMC)

The 6U Model 601 is an EMC chassis, which reduces the disturbances from EMI as follows:

- All gaskets, contacts, and contact surfaces are electrically conductive

- The mating surfaces of the EMC chassis and the EMC plug-in unit front panels and/or optional EMC filler panels are also conductive by use of gaskets/strips

- All chassis and plug-in contact surfaces are connected to a common chassis ground

Mating EMC gaskets and strips are used on the chassis, front panels of boards, and optional filler panels. An EMC gasket is attached to the left of the chassis (front view), and an EMC strip is attached to the right. Plugin boards have the corresponding mates on the opposite side (see figure 3).

Figure 3. EMC strip and gasket on chassis and cards

The EMC strip on the left side of the board mates with the EMC gasket attached to the chassis when it is plugged into the first slot. Each board mates together with corresponding gaskets/strips.

**Note** EMC gaskets/strips are in reverse order at the rear of the 6U chassis. That is, the EMC strip is on the left of the chassis and the EMC gasket is on the right. Consequently, rear transition boards are likewise in reverse order to the front-entry boards. The EMC gasket is on the left, and the EMC strip is on the right.

In addition, all aluminum and steel components of the subrack are surface treated and conductive. Top, bottom, sides and rear EMC covers provide mechanical protection and EMC shielding on the subrack. Retaining clips ensure conductive connection.

# Electrostatic discharge (ESD) protection

The 6U chassis provides ESD protection in compliance with IEEE 1101.10.

ESD contacts are embedded inside and in the front section of card guides for making early as possible contact with a discharge strip on one or both, the upper and/or lower edge of the plug-in board/module. Only the card

### 2 • Chassis specifications

guides located at the bottom rail of the chassis, both front and rear (when there is a transition module present in the chassis), contain the ESD clips. The ESD clip in the card guide is connected to the Chassis GND (ground).

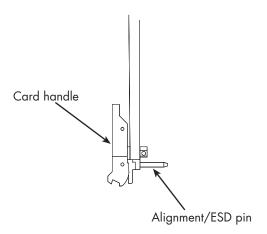

There is an alignment/ESD pin on the injector/ejector handle of boards (see figure 4).

Figure 4. Alignment/ESD pin on card handle

The alignment pin does the following:

- Ensures that the connectors are correctly aligned before they engage

- Provides solid/protected keying

- Provides board ESD contact

- Ensures that the EMC gasket is properly aligned (see "Electromagnetic compatibility (EMC)" on page 18)

- Ensures that when the board is inserted in the card guide, an integrated ESD clip discharges ESD from the board to the right vertical rail chassis ground.

# Materials specifications-Models 601 and 602 chassis

A list of the 6U model 601 chassis materials specifications is provided in table 3. A list of the model 602 chassis (which does not have a transition module) materials specifications is provided in table 4.

| Item                                  | Description                                                                                                                                                                    |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Physical                              | • Height–6U (10.50 in.)                                                                                                                                                        |  |  |

|                                       | <ul> <li>Width–19 in. (standard EIA rack mount)</li> </ul>                                                                                                                     |  |  |

|                                       | <ul> <li>Depth-12 in. maximum</li> </ul>                                                                                                                                       |  |  |

| DC interface                          | Rear DC interface panel includes dual ground bugs, –48V DC power<br>interface for N+1 redundant power operation, and connectors for<br>VRG, VRGRTN, -SEL VBAT and SEL VBATRTN. |  |  |

| Slot configuration                    | 21 slots (maximum) are on 0.80 in. centers, except power slots are                                                                                                             |  |  |

|                                       | 1.6 in. center<br>• Front—6U x 160 mm slots, Qty: 17                                                                                                                           |  |  |

|                                       | • REAR—6U x 80 mm slots, Qty: 17                                                                                                                                               |  |  |

| module keying and alignment           | 4HP module spacing, cardguide provides for keying and alignment pin in accordance with IEEE 1101.10, Section 6                                                                 |  |  |

| Card guides                           | Molded plastic with snap-in ESD contacts for both plug-in module and injector/ejector handle alignment pin                                                                     |  |  |

| Plug-in unit injector/ejector handles | Subrack dimensional format accepts modules with injector/ejector han-<br>dles as specified in IEEE 1101.10, Section 8                                                          |  |  |

| 6U chassis part no.                   | 60-00001                                                                                                                                                                       |  |  |

| 6U model no.                          | 6001                                                                                                                                                                           |  |  |

| Table 3. 6U Model 601 | chassis materials specifications |

|-----------------------|----------------------------------|

|-----------------------|----------------------------------|

The Model 602 chassis materials specifications are identical to Model 601 shown above, with the following differences noted in table 4.

| ltem                | Description                                                                                                                                                           |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical            | • Height–6U (10.50 in.)                                                                                                                                               |

|                     | • Width–19 in. (standard EIA rack mount)                                                                                                                              |

|                     | <ul> <li>Depth-7.25 in. maximum</li> </ul>                                                                                                                            |

| Slot configuration  | 21 slots (maximum) are on 0.80 in. centers, except power slots are 1.6 in. center. 17 slots are available when the Model 600 is configures with the 3U power supplies |

| 6U chassis part no. | 60-00002                                                                                                                                                              |

| 6U model no.        | 602                                                                                                                                                                   |

| Table 4. 6U Model 602 cl | hassis materials specifica | tions |

|--------------------------|----------------------------|-------|

|--------------------------|----------------------------|-------|

# **Patton Electronics' product interfaces**

One of the key features of a CompactPCI system is its interoperability with off-the-shelf boards that have been designed in compliance with the *PICMG CompactPCI 2.0 R2.1 Specification*. The Patton 6U chassis has this built-in interoperability. We believe, however, that the superior design and quality of Patton product families are your best bet for the 6U Chassis. The following Patton products mate with the 6U chassis.

## Model 5406 6U Redundant Backplane/Midplane

The 600 Series chassis is designed to accept Patton's backplane products which can be standard or custom designed per customer specifications. This manual contains a complete description of the Model 5406 Redundant Backplane/Midplane.

## Model 5250 Series Power Supply Module

Patton maintains the industry's highest power density footprint. The 3U power supply module provides stateof-the-art N+1 redundant power operation. The Model 5250 Power Supply Module delivers 200 watts in a 3U x 160mm x 8HP CompactPCI format. The 600 Series 6U chassis accepts up to four Model 5250 3U Power Supply Modules.

The Model 5250 is a modular, high power, CPCI plug-in module that supplies standard 3.3V, 5V and 12V DC voltages in a variety of configurations for use in electronic systems. The unit can be operated as either a wide range, AC input or 48V DC input and offers full mechanical compatibility with IEEE-1101.10. Each unit generates full power output with 300LFM (linear feet per minute) airflow. It features the latest CPCI power interface connector, and is fully hot-swappable.

Meets the requirements of: UL, CSA, FCC, NEBS and CE, UL1950, EN 60950, FCC Class B, EN 55022 Class B, NEBS-FR-2063 (1997).

## Model 5502 6U Alarm Interface Module

Patton's 6U x 80mm plug-in alarm interface module is designed to monitor and report alarm conditions to a system level controller or a remote alarm panel for high availability/reliability systems.

Inputs to the alarm module come from Patton's redundant power system and the two auxiliary connectors provided on the panel. Both the AUX 1 and AUX 2 connectors provide fully independent and isolated TTL level signals, which can be connected to any external monitoring device you desire.

All inputs can be configured as either Major or Minor alarm events. The Major and Minor Alarms provide a Normally open/Normally closed relay configuration that allows you the flexibility and isolation required to connect to an external controller or an external alarm panel.

This symbol and the CAUTION heading indicates a situation where equipment can be damaged by electrostatic discharge.

The unit is designed to comply with all electrical and mechanical requirements of IEEE 1101.10, UL, CSA, FCC, NEBS, and CE, UL 1950, EN 60950, FCC Class B, EN 55022, NEBS-FR-2063 (1997).

# Chapter 3 Installation checklist

# Chapter contents

| 6U quick set-up checkli | st |

|-------------------------|----|

|-------------------------|----|

# 6U quick set-up checklist

The 6U CPCI Model 5406 Backplane/Midplane & Chassis can be easily configured according to your system requirements. Due to the broad application possibilities, the following checklist is provided as a quick set-up guideline.

- 1. Select Signaling Environment—The signaling environment, called the Voltage Input/Output (V(I/O)), can be configured for 3.3V or 5V (factory default) signaling via power bugs, located at the rear, left-side of the backplane (See "Signaling Environment" on page 34).

- 2. Connect Frame Ground/Signal Ground (FG/SG)—You may opt to connect the FG/SG for EMC considerations and noise reduction, via power bugs, located at the rear, right-side of the backplane. The factory default is "no connect" (See figure 17 on page 43).

- **3.** Assign Shelf Address—For multi-shelf systems, each sub-rack bus segment can be assigned a shelf address via the S1 header, located at the rear, left-side of the backplane (See "Shelf enumeration bus P4 pins" on page 54).

- 4. Install 6U Chassis on Rack—the chassis front mounting flanges should be securely fastened to the rack with screws.

- **5.** Install Power Supply Modules—For N+1 power operation, install up to four Patton power supply modules configured for external DC (or other CPCI compatible power modules) at the front of the chassis.

- 6. Install Cards—Plug the system administration card(s) in the system slot(s) at the front of the 6U chassis, and up to 14 peripheral cards can be plugged into remaining slots. Plug alarm card in the left-hand slot at the back of the chassis, and plug transition cards in remaining slots, if needed.

- 7. Wire Rear Panel for Optional VRG/VBAT (See "Telecom power bus P4 pins" on page 53 and "Telecom ringing bus P4 pins" on page 54.)

- 8. Wire Rear Panel for Power (See "External power connections" on page 42.)

Due to possible injuries to people and severe damage to objects caused by electric shock, always wire for power as the last step.

# Chapter 4 System Architecture

# Chapter contents

| CompactPCI form factor                     | 54 |

|--------------------------------------------|----|

| Board front panels                         | 54 |

| Transition Boards                          | 55 |

| Pin and socket connectors                  | 57 |

| J1/P1 & J2/P2 connectors                   | 59 |

| J3/P3 through J5/P5 connector              | 60 |

| Reserved Pins                              | 60 |

| Power Pins                                 | 60 |

| Backplane Architecture                     | 61 |

| Signaling Environment                      | 62 |

| Changing the signaling environment voltage | 62 |

| Slot Designation                           | 64 |

| Bus segments                               | 65 |

| Backplane signals                          | 66 |

| Alarms                                     | 67 |

| Backplane power distribution               | 69 |

| External power connections                 | 70 |

| Backplane power bugs and connectors        | 71 |

| In-rack power connections                  | 72 |

| Front panel keying for power supplies      | 74 |

| Power decoupling                           | 74 |

| Hot-Swap Capability                        | 74 |

| Hot-Swap Insertion Sequence                | 75 |

| Hot-swap removal sequence                  | 76 |

| Keying of CPCI backplanes and boards       | 76 |

| Backplane connector keys                   | 76 |

| Front panel and cardguide keys             | 77 |

|                                            |    |

### 4 • System Architecture

# **CompactPCI form factor**

CompactPCI is flexible in the mechanical and connector area, using a passive backplane and plug-in daughterboards. The architecture is based on the IEC 1101.10 and 1101.11 Eurocard standard for the fixed 160mm depth (for front boards), but allows for two board heights:

- 3U—100mm high

- 6U—233.35mm high

This variety enables a wider variety of applications and industries. 3U, which is the minimum for CompactPCI as it accommodates the full 64-bit CompactPCI bus, is popular for embedded industrial automation applications, while 6U provides additional board real estate for more complex applications. 6U also provides more connectors for rear-panel I/O often needed in telecom products.

Eurocard boards offer a long list of advantages:

- Extensive board keying capabilities so that boards can only be plugged into appropriate slots

- ✓ Card guides for solid rear backplane connectors alignment

- Injector/ejector handles

- EMC compliance that minimizes electromagnetic interference

To provide maximum configuration flexibility, CompactPCI boards are inserted at the front of the chassis, with options for I/O connections to either the front and/or rear of the card. The cards are firmly held in position by their connector, card guides on both sides, and a face plate which solidly screws into the card cage.

### **Board front panels**

CompactPCI boards provide a front panel interface that is consistent with Eurocard packaging and compliant with IEEE 1101.10 (EMC panels). Ejector/injector handles are used on the boards. 3U boards only use one handle, while the 6U board uses two (see figure 5). Filler panels do not require handles.

Figure 5. Front panel—6U front-entry card

## **Transition Boards**

There are two types of boards:

- Front-entry boards (described in section "Board front panels")

- Rear-entry boards for rear-panel I/O

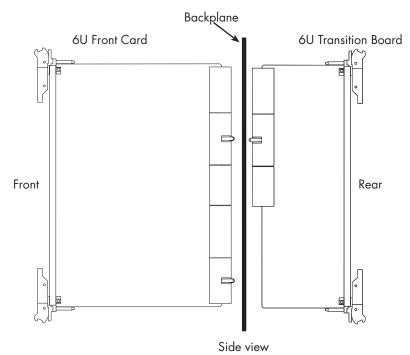

The front-entry boards may route I/O through the backplane. Backplanes that enable rear I/O are called often midplanes because the legs of the backplane connector's pins stick through the board to become pins for rear-

#### 4 • System Architecture

panel interconnections. An illustration of the front-entry board and rear-panel I/O board interface with the backplane/midplane is shown in figure 6.

Figure 6. Front/rear boards and backplane interface

Rear-panel I/O boards are 6U in height and are typically 80mm in depth. Other depths are allowed depending on the application requirements. The 6U chassis provides an 80mm transition module section. This section provides seventeen 6U x 80mm slots for an alarm card and/or other CPCI transition modules.

All front-entry board features (handles, keying, alignment pin, EMC, etc.) are also utilized on the rear-entry boards. The rear-panel I/O transition boards are "in-line" with the front-entry boards. This means that the front panels of rear-panel I/O transition boards are reversed (mirrored) from the front boards. The top handles are on the bottom and vice versa. The slot keying holes and hole labels in both the card guides and front panels are upside down compared to the front boards and card guides (see "Keying of CPCI backplanes and boards" on page 48 for more information on keying).

The same connector pin labeling sequence is used on the rear I/O transition boards as on the front boards, with the position numbers going from bottom to top. This is a mirror image of the front board's layout orientation. Using the same 1-for-1 pin mapping sequence eliminates confusion and I/O signal pin mapping problems. For example, pin A3 is the same on the front boards, on the rear I/O transition board, and on the backplane.

Rear-panel I/O transition boards may have active components in some applications. Power can be applied either through the I/O pins from the front board, or from the normal power and ground pins defined as part of the J1/P1 and J2/P2 connector pin assignments.

Rear I/O transition boards that only populate Rear J5 (RJ5) for the purpose of telephony I/O, must utilize a Type AB connector body on RJ5. This type of connector provides an integral alignment feature that avoids damage to the backplane pins during mating. Patton's 6U Model 5406 Backplane/Midplane complies with this requirement, providing a Type AB connector shroud on RP3, RP4, and RP5.

## Pin and socket connectors

The connection between boards and backplane is through a two-piece, 2mm connector. Backplanes use male (pin) connectors and plug-in boards use female (socket) connectors. This pin and socket connector offers greater reliability, particularly when subject to shock, vibration, or temperature variations.

These pin and socket connectors provide:

- Faster propagation times

- Reduced reflection at the bus/connector interface

- Lower noise

- Better impedance matching

- Higher mechanical stability

The connector is a 235-pin device, arranged in 47 rows of 5 pins, with a total of 220 pins (15 pins are lost to the keying area). The connector is shielded and devotes a large number of pins to ground. This reduces reflections, increases EMI immunity in noisy environments, and reduces ground bounce.

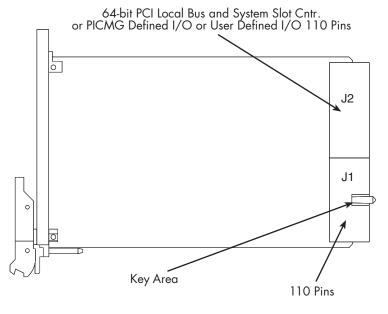

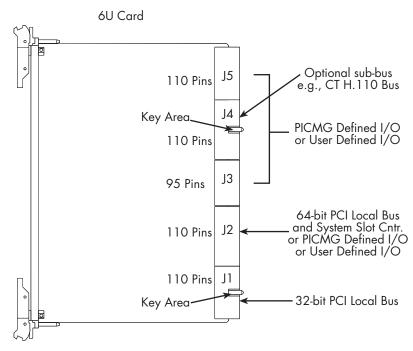

The fixed or male connector on the backplane is numbered P1-P5, starting at the bottom. The corresponding female connectors are also numbered from the bottom up as follows:

- 3U cards—J1-J2 (see figure 7 on page 30)

- 6U cards—J1-J5 (see figure 8 on page 30)

32-bit PCI Local Bus

Figure 7. J1 and J2 connectors on the 3U card

Figure 8. J1 through J5 connectors on the 6U card

3U and 6U cards use a single 220 pin connector for all power, ground, and all 32- and 64-bit PCI signals. This connector consists of two halves—the lower half (110 pins) is called J1/P1 and the upper half (also 110 pins) is called J2/P2. Twenty pins are reserved for future use. The connector is divided in J1/P1, a 25-row connector that includes voltage keying, and J2/P2, a 22-row connector without keying. The 6U card can have up to four additional connectors with a total of 315 pins, which can be used for a variety of purposes.

A system CPU uses J1 and J2, but 32-bit peripherals cards only need to use J1 for full CompactPCI functionality. J3 through J5 on 6U cards can be user-defined I/O. Optional buses, such as the CT H.110 bus, use the J4 position.

## J1/P1 & J2/P2 connectors

The CompactPCI bus spans the J1/P1 & J2/P2 connectors, with 32-bit PCI implemented on J1/P1 and full 64-bit PCI implemented on J2/P2 on the 6U Model 5406 Backplane/Midplane. J1/P1 is always devoted to 32-bit PCI in CompactPCI systems, however, use of J2/P2 for 64-bit PCI can be optional. For instance, in a 3U system, J2/P2 may be defined for user I/O, or sub-buses like the CT H.110 bus. J2 is always used on system slot boards to provide arbitration and clock signals for peripheral boards.

|    |     |           | Compucii Ci |          | r/jr ana r | <u> </u>  |     |           |

|----|-----|-----------|-------------|----------|------------|-----------|-----|-----------|

| 22 | GND | GA4       | GA3         | GA2      | GA1        | GA0       | GND | P2        |

| 21 | GND | CLK6      | GND         | RSV      | RSV        | RSV       | GND | /J2       |

| 20 | GND | CLK5      | GND         | RSV      | GND        | RSV       | GND |           |

| 19 | GND | GND       | GND         | RSV      | RSV        | RSV       | GND | CONNECTOR |

| 18 | GND | BRSVP2A18 | BRSVP2B18   | BRSVPC18 | GND        | BRSVPE18  | GND | N N       |

| 17 | GND | BRSVP2A17 | GND         | PRST#    | REQ6#      | GNT#6     | GND | DLC       |

| 16 | GND | BRSVP2A16 | BRSVP2B16   | DEG#     | GND        | BRSVP2E16 | GND | R         |

| 15 | GND | BRSVP2A15 | GND         | FAL#     | REQ5#      | GNT5#     | GND |           |

| 14 | GND | AD[35]    | AD[34]      | AD[33]   | GND        | AD[32]    | GND |           |

| 13 | GND | AD[38]    | GND         | V(I/O)   | AD[37]     | AD[36]    | GND |           |

| 12 | GND | AD[42]    | AD[41]      | AD[40]   | GND        | AD[39]    | GND |           |

| 11 | GND | AD[45]    | GND         | V(I/O)   | AD[44]     | AD[43]    | GND |           |

| 10 | GND | AD[49]    | AD[48]      | AD[47]   | GND        | AD[46]    | GND |           |

| 9  | GND | AD[52]    | GND         | V(I/O)   | AD[51]     | AD[50]    | GND |           |

| 8  | GND | AD[56]    | AD[55]      | AD[54]   | GND        | AD[53]    | GND |           |

| 7  | GND | AD[59]    | GND         | V(I/O)   | AD[58]     | AD[57]    | GND |           |

| 6  | GND | AD[63]    | AD[62]      | AD[61]   | GND        | AD[60]    | GND |           |

| 5  | GND | C/BE[5]#  | GND         | V(I/O)   | C/BE[4]#   | PAR64     | GND |           |

| 4  | GND | V(I/O)    | BRSVP2B4    | C/BE[7]# | GND        | C/BE[6]#  | GND |           |

| 3  | GND | CLK4      | GND         | GNT3#    | REQ4#      | GNT4#     | GND |           |

| 2  | GND | CLK2      | CLK3        | sysen#   | GNT2#      | REQ3#     | GND |           |

| 1  | GND | CLK 1     | GND         | REQ1#    | GNT1#      | REQ2#     | GND |           |

|    |     |           |             |          |            |           |     |           |

Table 5. CompactPCI pinouts on P1/J1 and P2/J2

|                     |                                |                          | 1                  |                             | , ,               |                           |                   |       |

|---------------------|--------------------------------|--------------------------|--------------------|-----------------------------|-------------------|---------------------------|-------------------|-------|

| 25                  | GND                            | 5V                       | REQ64#             | ENUM#                       | 3.3V              | 5V                        | GND               | Ρl    |

| 24                  | GND                            | AD[1]                    | 5V                 | V(I/O)                      | AD[0]             | ACK64#                    | GND               | ll/   |

| 23                  | GND                            | 3.3V                     | AD[4]              | AD[3]                       | 5V                | AD[2]                     | GND               |       |

| 22                  | GND                            | AD[7]                    | GND                | 3.3V                        | AD[6]             | AD[5]                     | GND               | CONNE |

| 21                  | GND                            | 3.3V                     | AD[9]              | AD[8]                       | M66EN             | C/BE[0]#                  | GND               | ZE    |

| 20                  | GND                            | AD[12]                   | GND                | V(I/O)                      | AD[11]            | AD[10]                    | GND               | CTOR  |

| 19                  | GND                            | 3.3V                     | AD[15]             | AD[14]                      | GND               | AD[13]                    | GND               | R     |

| 18                  | GND                            | SERR#                    | GND                | 3.3V                        | PAR               | C/BE[1]#                  | GND               |       |

| 17                  | GND                            | 3.3V                     | SDONE              | SBO#                        | GND               | PERR#                     | GND               |       |

| 16                  | GND                            | DEVSEL#                  | GND                | V(I/O)                      | STOP#             | LOCK#                     | GND               |       |

| 15                  | GND                            | 3.3V                     | FRAME#             | IRDY#                       | GND               | TRDY#                     | GND               |       |

| 12-14               | Key Ar                         | ea                       | •                  | •                           | •                 |                           |                   |       |

| 11                  | GND                            | AD[18]                   | AD[17]             | AD[16]                      | GND               | C/BE[2]#                  | GND               |       |

| 10                  | GND                            | AD[21]                   | GND                | 3.3V                        | AD[20]            | AD[19]                    | GND               |       |

| 9                   | GND                            | C/BE[3]#                 | IDSEL              | AD[23]                      | GND               | AD[22]                    | GND               |       |

| 8                   | GND                            | AD[26]                   | GND                | V(I/O)                      | AD[25]            | AD[24]                    | GND               |       |

| 7                   | GND                            | AD[30]                   | AD[29]             | AD[28]                      | GND               | AD[27]                    | GND               |       |

| 6                   | GND                            | REQ#                     | GND                | 3.3V                        | CLK               | AD[31]                    | GND               |       |

| _                   |                                |                          |                    |                             |                   |                           |                   |       |

| 5                   | GND                            | BRSVP1A5                 | BRSVP1B5           | RST#                        | GND               | GNT#                      | GND               |       |

| <mark>5</mark><br>4 | <mark>GND</mark><br>GND        | BRSVP1A5<br>BRSVP1A4     | BRSVP1B5<br>GND    | <mark>RST#</mark><br>V(I/O) | GND<br>INTP       | <mark>GNT#</mark><br>INTS | GND<br>GND        |       |

| 4<br>3              |                                |                          |                    |                             |                   |                           |                   |       |

| 4                   | GND                            | BRSVP1A4                 | GND                | V(I/O)                      | INTP              | INTS                      | GND               |       |

| 4<br>3              | GND<br>GND                     | BRSVP1A4<br>INTA#        | GND<br>INTB#       | V(I/O)<br>INTC#             | INTP<br>5V        | INTS<br>INTD#             | GND<br>GND        |       |

| 4<br>3<br>2         | GND<br><mark>GND</mark><br>GND | BRSVP1A4<br>INTA#<br>TCK | GND<br>INTB#<br>5V | V(I/O)<br>INTC#<br>TMS      | INTP<br>5V<br>TDO | INTS<br>INTD#<br>TDI      | GND<br>GND<br>GND |       |

Table 5. CompactPCI pinouts on P1/J1 and P2/J2 (Continued)

## J3/P3 through J5/P5 connector

J3/P3 through J5/P5 connectors, available only in 6U systems, are generally defined for user I/O. However, sub-bus interconnects (for example, CT H.110 bus) can be configured on the J4/P4 connector.

## **Reserved Pins**

There are bused and non-bused reserved pins as noted below:

- The BRSVPxxx signals SHALL be bused between connectors and are reserved for future CompactPCI definition.

- The RSV signals are non-bused signals that SHALL be reserved for future CompactPCI definition.

## **Power Pins**

The 6U Model 5406 Backplane/Midplane signaling environment is factory-defaulted at 5V. However, it has a customer-selectable option to change it to 3.3V by changing the jumper on the power bugs located at the back of the backplane (see "Signaling Environment" on page 34). All connectors on Patton's 6U Model 5406 Backplane/Midplane provide pins for +5V, +3.3V, +12V and -12V operating power.

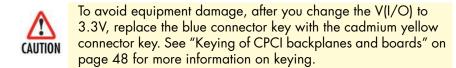

In addition, there are power pins labeled +V(I/O). The V(I/O) power pins on the connector are used to power the buffers on the peripheral boards, allowing a card to be designed to work in either interface. CompactPCI supports this dual-interface scheme by utilizing backplane connector keying (see "Keying of CPCI backplanes and boards" on page 48 for more information).

## **Backplane Architecture**

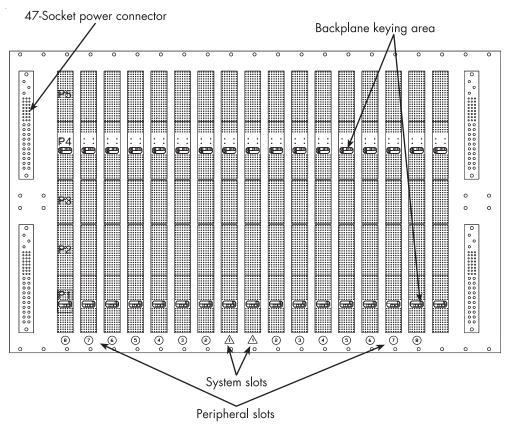

The Model 5406 Backplane/Midplane provides two electrically separate, CompactPCI bus segments. Each CPCI bus segment is composed of eight 6U board locations (at 33 MHz) with 20.32 mm (0.8 inch) board center-to-center spacing.

There are also four 47-socket Positronics power connectors, two on the left and two on the right, to mount Patton's Power Supply Modules (3U x 160mm) —configured for external DC input—or other CPCI compatible power modules. The connectors meet requirements specified in the *PICMG 2.11, R1.0 CompactPCI Power Interface Specification.* Refer to "In-rack power connections" on page 44 for a description of these features.

The front view of the 6U Model 5406 Backplane/Midplane is shown in figure 9.

Figure 9. Front view of backplane

#### 4 • System Architecture

## Signaling Environment

The 6U Model 5406 Backplane/Midplane provides for either a 5V or 3.3V signaling environment.

PCI allows for two types of buffer interfaces for interboard connection. The V(I/O) power pins on the connector are used to power the buffers on the peripheral boards, allowing a card to be designed to work in either interface. These are called universal boards. It should be noted, that backplanes are never universal. The V(I/O) level distributed on the backplane is either 5.0V or 3.3V. It is only possible that boards can be tolerant of either voltage levels, and considered universal.

The factory default setting for the 6U Model 5406 Backplane/Midplane is for the 5V signaling environment (denoted by the brilliant blue connector key). The signaling environment (denoted by the cadmium yellow connector key), called the Voltage Input/Output (V(I/O)), can be configured for 3.3v signaling via a power bug located at the back of the backplane.

Changing the signaling environment voltage

The following outlines the steps to change the default setting of 5V to 3.3V.

Due to a safety hazard, only rewire the signaling environment prior to wiring the board with external power connections.

1. Using a flat-head screwdriver, remove the four screws (two on top, two on bottom) on the left, rear panel of the chassis (see figure 10).

Figure 10. Removing left rear panel of chassis

600 Series 6U CPCI Chassis User Manual

**2.** Using a phillips screwdriver, remove the screw and wire from the 5V ring terminal (labeled J16) (see figure 11). Do not remove the wire from the V(I/O) terminal (labeled J17).

Figure 11. Removing 5V ring terminal screw and wire

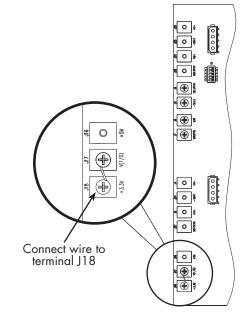

**3.** Keeping the wire connected to the V(I/O) terminal, connect the other end of the wire to the +3.3V terminal (labeled J18), securing the screw in the ring terminal with a phillips screwdriver (see figure 12).

Figure 12. Connecting 3.3V ring terminal screw and wire

### **Slot Designation**

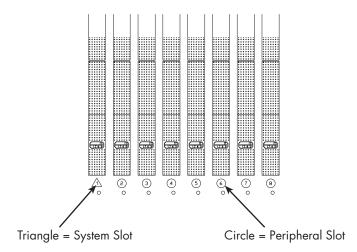

Consistent with CompactPCI specifications, the CPCI bus segment consists of one system slot, and seven peripheral slots. The system slot is denoted with a "triangle" compatibility glyph, and the seven peripheral slots are marked with a "circle". The 6U CPCI Model 5406 backplane/midplane has two, electrically separate CPCI bus segments. In CPCI bus segment one, the system slot is on the right, and in CPCI bus segment two (see figure 12), the system slot is on the left (see also figure 9 on page 33, which shows both bus segments together).

Figure 13. Slot compatibility glyphs (segment 2 shown)

The system slot provides arbitration, clock distribution, and reset functions for all boards on the segment. The system slot performs system initialization by managing each local board's IDSEL signal. The peripheral slots may contain simple boards, intelligent slaves, or PCI bus masters.

CompactPCI defines slot numbering based on the concept of physical and logical slots. Physical backplane slots are designated 1, 2, 3, through N, where N is the number of slots. Physical slot numbering starts at the left on the 6U Model 5406 Backplane/Midplane (see figure 14).

Slot #: 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21

Figure 14. 6U backplane configuration

Logical slot numbers are defined by the IDSEL signal and associated address used to select the slot. Logical numbers are used in the nomenclature to define the physical outline of a connector on a bus segment. Logical and physical slot numbers may not always coincide.

Each slot may be implemented with 1 to 5 connectors numbered P1–P5, starting from the bottom of the board.

#### Bus segments

The 6U Model 5406 Backplane/Midplane is configured for 64-bit/32-bit interoperability. For example, a 32-bit processor and peripherals can be plugged into a 64-bit backplane. Because the backplane is passive, it is possible to have a 32-bit CPU in a system working with 64-bit peripherals.

The system slot uses J1/P1 and J2/P2 to allow the arbitration and clock signals to be connected to the backplane from the system slot board. Connectors on the backplane utilize pin staging to enable hot swapping of boards. (See Hot-Swap Capability on page 52 for more information.)

The CompactPCI bus segment on the 6U Model 5406 Backplane/Midplane bus all signals in all slots within the segment except the slot specific signals: CLK; REQ#; and GNT#. Each logical slot also has a unique IDSEL signal connected to one of the upper ADxx signals for configuration (plug and play) decoding. The 6U Model 5406 Backplane/Midplane implements the modular power supply connector that provides connection

#### 4 • System Architecture

for the power supply signals DEG# and FAL# at the system slot. (See table 6 for more information on the backplane signals.)

#### **Backplane signals**

CompactPCI utilizes PCI signals as defined by the PCI Local Bus Specification, with some additional signals. The additional signals enhance system operation, and do not affect the PCI signals. See table 6 for a list of the backplane signals with a brief description.

**Note** See PICMG, 2.0, R2.1 CompactPCI, Specification for more information.

| Signal       | Description                                                                                                                                                                                                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0-CLK4    | Backplane clock routing supports CLKO-CLK4. CLK5-CLK6 provided by the system slot board are not routed on the backplane.                                                                                                                                                                                                          |

| IDSEL        | The PCI signal IDSEL is used to provide unique access to each logical slot for configuration purposes. The backplane makes the connection to IDSEL at each logical slot's connector with minimum trace length.                                                                                                                    |

| REQ#/GNT#    | Request/grant signals. the system slot on the backplane supports the full complement of REQ#/GNT# signals.                                                                                                                                                                                                                        |

| PRST#        | Push button reset—an active low true TTL signal generated by a switch closure or an open-<br>collector driver. It is used to reset the system slot board, which in turn would reset the rest of<br>the system using the PCI RST# signal.                                                                                          |

| DEG#/FAL#    | <ul> <li>Power supply status.</li> <li>DEG#—derating signal—an output from the power supply to indicate that the supply is beginning to derate its power output.</li> </ul>                                                                                                                                                       |

|              | • FAL#—supply fail signal—an output from the power supply to indicate that it has failed.                                                                                                                                                                                                                                         |

| SYSEN#       | System slot identification—this pin is grounded on the backplane at the system slot so the board may identify installation into the system slot. This pin is not connected on the backplane for the remaining slots.                                                                                                              |

| ENUM#        | system enumeration—this low true TTL open-collector signal is driven by hot swap compatible<br>boards after insertion and prior to removal. the system master uses this interrupt signal to<br>force software to interrogate all boards within the system for resource allocation regarding I/<br>O, memory, and interrupt usage. |

| GA0/GA4      | Geographic addressing –the GAO-4 signals are available on the top five pins of the J2/P2 connector on backplanes that implement 64-bit. 32- and 64-bit boards use it to provide a unique differentiation based upon which physical slot the board has been inserted.                                                              |

| INTA# -INTD# | PCI interrupt binding of the BIOS setup program require backplane assignments from the sys-<br>tem slot interrupt pins INTA#—INTD# to the logical board slot interrupts. Refer to the "Com-<br>pactPCI Specification", PICMG 2.0, R2.1 for backplane assignments.                                                                 |

| INTP -INTS   | Legacy IDE interrupt support—two additional non-PCI interrupts are defined for IDE boards.<br>These signals are active high TTL level signals and do not have to meet the PCI electrical<br>buffer characteristics. They are provided to ease the transition from compatibility mode to<br>native mode PCI IDE operation.         |

Table 6. Backplane signals

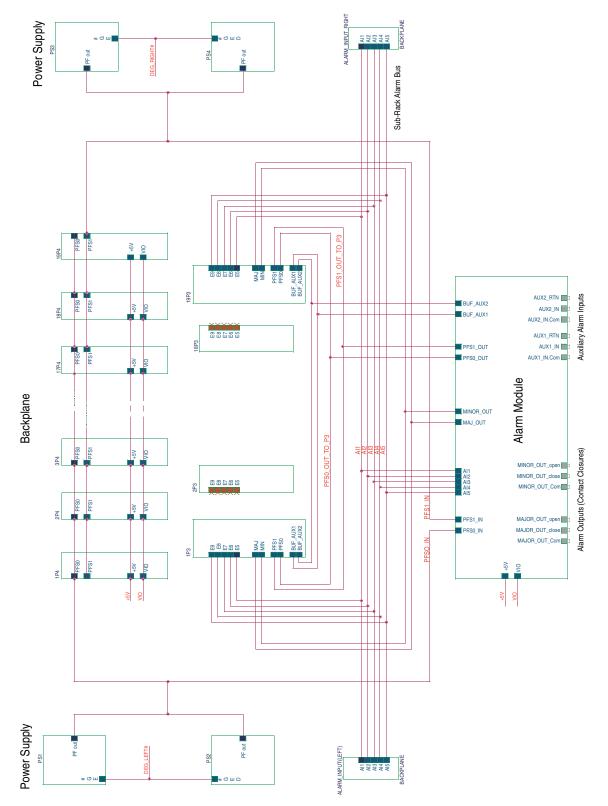

#### Alarms

In CompactPCI, systems the Alarm Card is designed to monitor and report alarm conditions to a system level controller or a remote alarm panel. The connections from the Alarm Card to the system level controller are passed through the connector. No backplane routing is required. However, backplane routing may be required for routing external sensors to the Alarm Card. This is called a Subrack Alarm Bus. The 6U Backplane/Midplane provides this type of Subrack Alarm Bus.

Five signals (AI1-AI5) from the 6U backplane are entered from the P3 connector to the Alarm Card. The possible monitoring conditions are:

- Airflow sensor

- Temperature sensor in fan tray

- Watchdog on Voice Cards (CT Bus)

- Watchdog on Switch Cards (CT Bus)

- Watchdog on Admin Card

The five alarm signals from the backplane can be configured using Patton's Model 5502 Alarm Module, to output as Major or Minor Alarms. Furthermore, the alarm outputs can be configured with time-outs from 1-9 minutes. (See "Model 5502 6U Alarm Interface Module" on page 22 for more information.)

Patton can customize the internal alarm signals per customer requirements. Or, backplanes can be customized to disconnect the alarm bus signals from P3. When disconnected, P3 is then standard I/O.

The Backplane Alarm wiring is shown in figure 15 on page 40.

#### 4 • System Architecture

Figure 15. Backplane alarm wiring detail

#### **Backplane power distribution**

Power is distributed in a CompactPCI system via the backplane. The backplane provides standard direct current (DC) supply voltages as specified in table 7 below

| Mnemonic | Description | Nominal Value | Tolerance | Max. Ripple        |

|----------|-------------|---------------|-----------|--------------------|

| 5V       | +5VDC       | 5.0V          | ±5%       | 50 MV <sup>a</sup> |

| 3.3V     | +3.3VDC     | 3.3V          | ±5%       | 50 MV <sup>a</sup> |

| +12V     | +12VDC      | 12.0V         | ±5%       | 50 MV <sup>a</sup> |

| -12V     | -12VDC      | -12.0V        | ±5%       | 50 MV <sup>a</sup> |

| GND      | GROUND      |               |           |                    |

|  | Table | 7 | Power | specifications |

|--|-------|---|-------|----------------|

|--|-------|---|-------|----------------|

a. Maximum ripple is very difficult to accurately measure and therefore requires good measurement techniques. Measurement should be made at full load at 20 MHz bandwidth with a 22mF capacitor located at the measurement point.

The Model 5406 Backplane/Midplane & Chassis provides two types of power connections for N+1 power operation:

- External power connections

- In-rack power connections

#### 4 • System Architecture

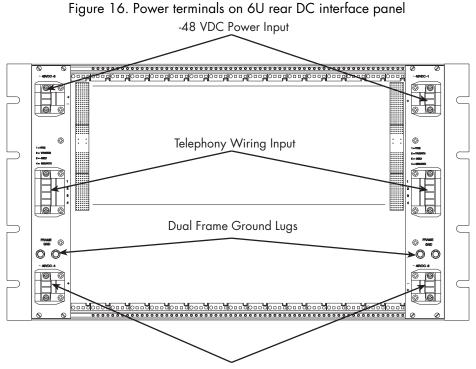

#### **External power connections**

The chassis provides a rear DC interface panel with -48V DC power interfaces for N+1 power operation and dual ground bugs, as shown in figure 16 below. The connectors are described in table 8.

-48 VDC Power Input

| Table 8. Description of rear | interface panel connectors |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

| ltem                   | Description                                                                                                                                                                                                                                                                                                              |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -48 VDC power terminal | DC rear-entry module accepts 36 VDC-72 VDC @ 10 Amp max input via Phoenix connector. Polarity should be applied as marked (negative—top position, positive—bottom position). Each connector is independent and designed to power one 3U power supply module. there are four connectors provided for n+1 power operation. |

| VRG                    | Telecom power source—the VRG and VRGRTN contacts connect a ring voltage source, such as a central office ring signal to the backplane. This is typically 60VRMS—170VRMS, 16HZ to 72HZ.                                                                                                                                   |

| VRGRTN                 | Telecom power source return                                                                                                                                                                                                                                                                                              |

| -SEL VBAT              | Safety extra low voltage or "short loop" battery (voltage within SELV limits) the –<br>SEL VBAT and SEL VBAT RTN connectors connect an isolated power source to the<br>backplane for use in powering telephony lines. They are not intended to power the<br>3U power supplies.                                           |

| SEL VBAT RTN           | Short loop battery return (voltage within SELV limits)                                                                                                                                                                                                                                                                   |

| Table 8. De | escription of rear | interface panel | connectors | (Continued) |

|-------------|--------------------|-----------------|------------|-------------|

|-------------|--------------------|-----------------|------------|-------------|

| ltem        | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground bugs | The dual-frame ground bugs must be used to connect the chassis to earth ground<br>on dc interfaces. Failure to do this will cause excessive RF emissions and could<br>possibly create a safety hazard. The double ground bug meets nebs and will<br>accept AMP part# 606209-1. NEBS requires a double bug on DC chassis to<br>ensure that the ground connection will not rotate and become loose. |

#### The dual frame ground lugs on DC interfaces must be used to connect the chassis to earth ground. Failure to do this will cause excessive RF emissions and could possibly create a safety hazard.

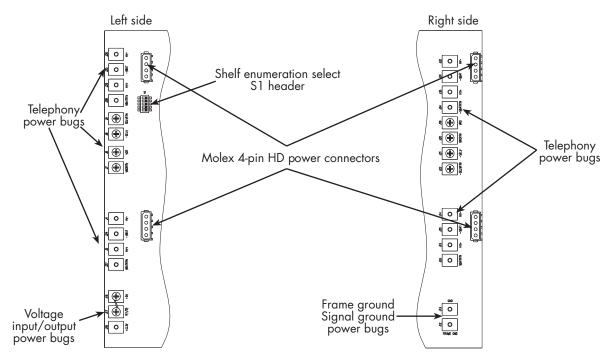

#### Backplane power bugs and connectors

The 6U transition module provides phoenix connectors for the -48V DC power interfaces, discussed in the previous section (figure 16 on page 42). However, if you purchased the 6U Model 5406 Backplane/Midplane without the chassis, there are different styles of connectors (figure 17).

Figure 17. Internal backplane power bugs and connectors

#### 4 • System Architecture

Table 5 provides a description of the internal backplane connectors shown in Figure 13 above.

| ltem                         | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1—P4                        | DC rear-entry module accepts 36 VDC–72 VDC @ 10 Amp max input via<br>molex 4-pin connectors. polarity should be applied as marked. the male<br>(pin) connector is on the backplane, and the mate is the female (socket)<br>connector. each connector is independent and designed to power one 3U<br>power supply module. there are four connectors provided for N+1 power<br>operation. |

| J4–J9, J14,<br>J15, J19–J22, | <ul> <li>No. 6 X 3/8 in. screw-ring terminal power bugs that you hard-wire. ±<br/>HV (high voltage) requires 14 GA wire.</li> </ul>                                                                                                                                                                                                                                                     |

| J24–J35                      | <ul> <li>Refer to Table 8 on page 42 for descriptions of VRG (J1), VRGRTN<br/>(J2), -SEL VBAT(J3) and SEL VBATRTN (J4).</li> </ul>                                                                                                                                                                                                                                                      |

|                              | -VBAT (J5)—Telecom power source                                                                                                                                                                                                                                                                                                                                                         |

|                              | <ul> <li>VBATRTN (J6)—Telecom power source return</li> </ul>                                                                                                                                                                                                                                                                                                                            |

| J12—J13                      | No. 6 X 3/8 in. screw-ring terminal power bugs that you hard-wire.<br>Depending on the environment, J12—frame ground (FG) and J13—signal<br>ground (SG) and can be wired together for EMC considerations and noise<br>reduction. (See also "Electromagnetic compatibility (EMC)" on page 18)                                                                                            |

| J16-J18                      | No. 6 X 3/8 in. screw-ring terminal power bugs that you hard-wire to change the voltage input/output From 5V (factory default) to +3.3v. (See "Signaling Environment" on page 34)                                                                                                                                                                                                       |